I processori di AMD basati sull’architettura Bulldozer a 32 nanometri dovrebbero essere annunciati entro la fine di settembre (la data più probabile è il 19). Nel frattempo sono circolate diverse informazioni sui nomi dei primi modelli con quattro, sei e otto core, sulle frequenze di clock e sulle tecnologie integrate. Il socket sarà il nuovo AM3+, il controller dual channel di memoria supporterà moduli DDR3 a 1.866 MHz e tutti i modelli integreranno 8 MB di cache L3.

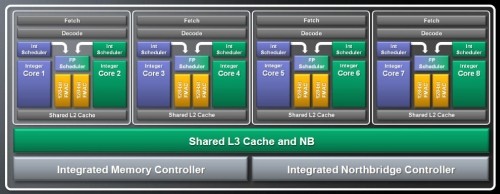

AMD definisce il componente base dell’architettura come “modulo Bulldozer“, che corrisponde ad una CPU dual core. Quindi in una CPU quad core ci sono due moduli, mentre in una CPU a otto core, i moduli sono quattro. In un modulo sono presenti una unità in virgola mobile (FPU) a 256 bit (ogni core vede 128 bit), due unità a 128 bit per l’esecuzione delle istruzioni sugli interi, quattro pipeline e 16 KB di cache dati L1 per ogni core. La cache L2 da 2 MB invece è condivisa tra i due core, così come la cache istruzioni L1 da 64 KB, gli stadi di prelievo (Fetch) e di decodifica (Decode) delle istruzioni.

Nelle precedenti architetture di AMD, ogni core aveva le proprie unità Fetch e Decode, la propria cache L2 e la propria FPU. L’azienda di Sunnyvale ha scelto di condividere queste unità tra i due core per diverse ragioni. Innanzitutto, si ottiene una riduzione della dimensione del chip (meno transistor), ma anche un diminuzione dei consumi, del calore generato e infine un risparmio dei costi produttivi. AMD ha stimato che la FPU viene utilizzata con una frequenza inferiore al 50%, per cui la scelta di una FPU condivisa è sembrata pertinente. L’azienda dichiara che ogni modulo fornisce prestazioni simili ad una “vera” CPU dual core, ma con un’area di silicio ridotta del 50%.

Bulldozer integra funzionalità particolari per ridurre la latenza e per allocare dinamicamente le risorse tra i core. Inoltre, quando un solo core è attivo, esso ha accesso completo a tutte le risorse condivise. Lo svantaggio principale dell’approccio di AMD è l’impossibilità di gestire la frequenza dei singoli core. La tecnologia Turbo Core 2.0 e il Power Gating infatti agiscono a livello di modulo, quindi è possibile incrementare la frequenza di due core alla volta e disattivare i core rimanenti per risparmiare i consumi.

Con Bulldozer, finalmente AMD supporterà anche le istruzioni SSE4.1 e 4.2, sfruttate dalle applicazioni multimediali, e le istruzioni AVX e AES, introdotte da Intel con le architetture Sandy Bridge e Westmere.